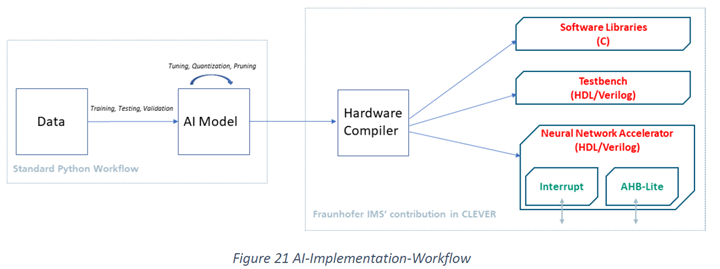

Fraunhofer IMS is pushing the boundaries of AI computation by developing a hardware compiler for neural networks in the CLEVER Project. This innovative framework translates Python (TensorFlow) models directly into hardware accelerators (Verilog HDL), setting new standards for efficiency in edge-AI solutions.

🔧 Key Features:

- RISC-V AIRISC Processor Integration: The accelerators will interface seamlessly with the 32-bit AIRISC microcontroller via an AHB-Lite bus, enabling efficient communication and performance.

- C-Libraries for Easy Integration: Automatically generated libraries ensure smooth software integration.

- Accelerator Targets: Designed for CNN-based tasks, perfect for time series analysis and image classification.

📈 Development Highlights:

- Leveraging Xilinx FPGA as a development platform for co-integration and testing.

- Supporting both wired (UART, SPI) and wireless (BLE, Wi-Fi) interfaces through PMOD extension boards.

- A hardware workflow that ensures optimized AI models in Python are seamlessly converted into hardware accelerators.

🌱 Real-World Applications:

The AIRISC processor’s resource-efficient design is ideal for edge-AI use cases like Agricolus, where it could power precise image classification for smart agriculture or time series analysis for eco-farm optimization.

💡 Fraunhofer IMS is paving the way for practical, scalable AI solutions for embedded systems—making AI hardware smarter, faster, and more accessible.

📌 Stay tuned for updates from #CLEVERProject!